Over the last few posts, we've been looking at the digital side of the POT analog to digital converters. In reference to the above quote, the reason I was perplexed by the section of the die shot that the POT_X signal is coming from is because it's analog in nature. Up until this point, the vast majority of the sections of die shot we have been looking at have been digital logic. Over the past couple of years, I've become quite familiar with recognising digital structures, but not analog. Electronics being a hobby for me, and digital being the primary focus, I don't have a good understanding of the analog side.lance.ewing wrote:The POT_X input on the left has come from a section of the die shot that we haven't looked at yet, but it comes from the direction of the POT X bonding pad after having passed through some circuitry that currently I'm a bit perplexed by (I'm wondering if it relates to the amplifier symbols on the block diagram).

But despite my lack of experience, we already have a fair idea of what to expect with the 6561 POT ADC circuits. We can start with what the datasheet tells us:

(Emphasis added)These input pins are used to convert potentiometer position into a microprocessor readable 8 bit HEX number. This is accomplished by a simple RC time constant integration technique. The potentiometer is used to charge an external capacitor tied to the pot pin.

So this tells us that the integration is a simple RC time constant mechanism, and that the capacitor is external. A simple RC integrator looks like this:

(source: https://www.electronics-tutorials.ws/rc ... rator.html)

...as a lot of you will already be very familiar with. And this diagram looks like what we have connected to the 6561 POT pins on the VIC 20 circuit board when a paddle is connected to the joystick port. Obviously without the paddle connected, it isn't an RC integrator. The capacitor is on the VIC 20 circuit board, and the variable resistor in the paddle.

I found the following article that is worth a read. It describes a mechanism for using a digital input to an MCU to read an analog signal. All it uses is an RC integrator circuit, and the MCU counts how long it takes the digital input to go HIGH, and then discharges it by pulling the pin low.

https://www.microcontrollertips.com/mcu ... thout-adc/

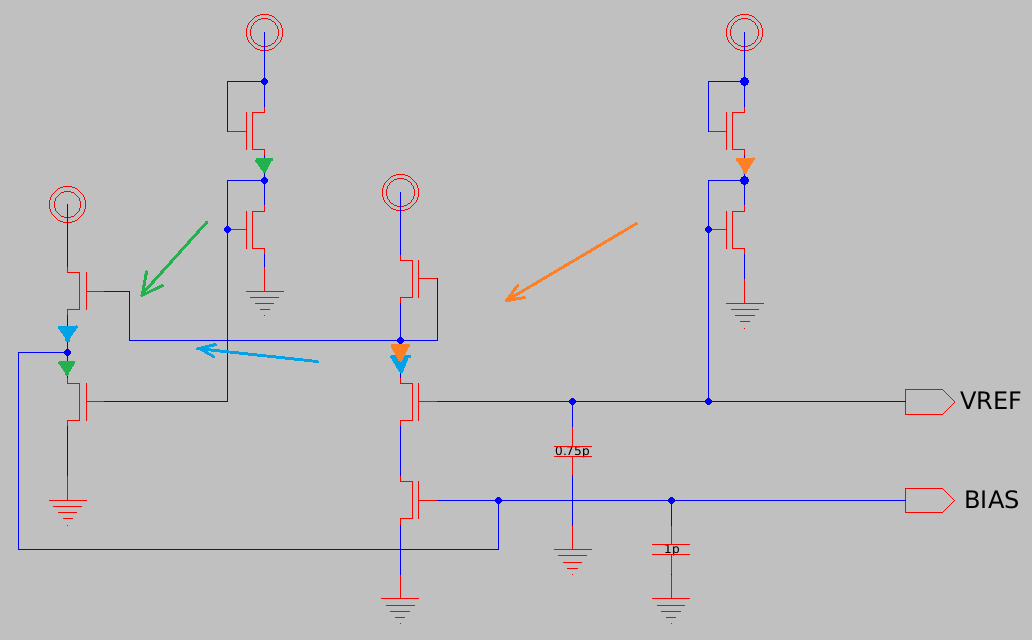

I've been reading up on ADC designs over the past few days, and the design that seems closest to what we see with the 6561 is the single slope ADC. I've discounted the dual slope ADC because there doesn't appear to be anything that switches between a Vin and Vref. The Vref is internal to the 6561 (in fact I believe I've identified where it is generated) and we just have the input coming in. This input though is the input after the RC integrator (keep this in mind when looking at the next diagram).

A single slope ADC is usually shown to look something like this:

(source: https://www.hardwaresecrets.com/how-ana ... c-works/8/)

I was a bit hesitant to include the above diagram, because it isn't quite what is happening with the 6561. I couldn't find a closer match though. Instead let's view the above as a more classic single slope ADC as a means to introduce the concept. The diagram above shows the Vref being used with the integrator, but in the case of the 6561, it seems that the integrator (the RC integrator mentioned above) is used with the Vin. Instead the internally generated Vref within the 6561 seems to be one of the direct inputs to the comparator, and is fixed, whereas the Vin goes through the external RC integrator and then into the internal comparator.

It is worth talking a bit about the simple slope ADC diagram above. The box labelled "Output Buffer" is the equivalent of the 6561 POTX or POTY register (CR8 and CR9) and the Counter is the 8-bit counter that we have already identified in the 6561. We can see from the diagram that there is a clock signal that increments the Counter. When the comparator output changes, it clocks the transfer of the current Counter value into the lower box. The diagram above also shows the comparator clearing the Counter, but this isn't what happens in the 6561. Instead the counter will keep counting up to its maximum value (at which point it stops counting) and will reset when the vertical counter is next at a multiple of 8. The above diagram also shows the comparator change in output discharging the capacitor, but in the 6561 that doesn't happen and instead it is likewise discharged when the vertical counter is next at a multiple of 8.

Remember, the 6561 is using an external RC integrator rather than a op amp integrator. On every 8th line, it pulls the POT pin low to discharge the external capacitor.

In the next post, we're going to start looking for the comparator, which will involve identifying differential pairs, a constant current source, and reference voltage (Vref).