Kakemoms wrote:Ok, so basically they are stored in flip-flops..or at least it looks that way. I do not understand the circuit you linked to though.. it looks like it only can put the circuit into one state (W high), while the other (W low) does not make much sense to me.. Maybe you could explain that one a little further?

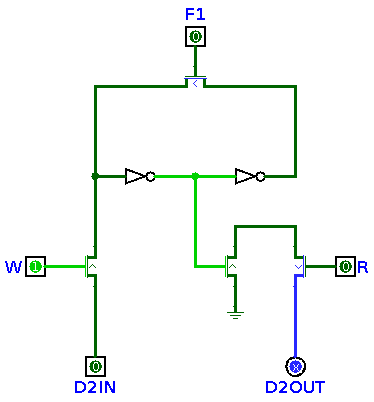

The following diagram shows the same circuit but with the inverters replaced with the inverter symbol (and I've also split D2 into D2IN and D2OUT, because Logisim doesn't seem to support a dual purpose input/output):

- control_register_cell_logisim.png (3 KiB) Viewed 6537 times

The design is similar to a couple of circuits that are discussed in the Mead/Conway "Introduction to VLSI Systems" book that I've referred to previously:

http://ai.eecs.umich.edu/people/conway/ ... -sided.pdf

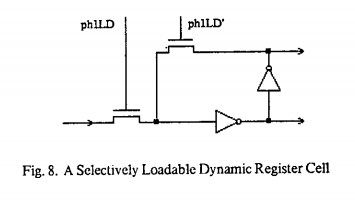

From chapter 3, Fig 8:

- register_cell_mead_conway_sect3_fig8.png (14.53 KiB) Viewed 6537 times

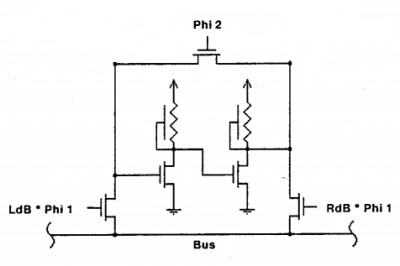

And from chapter 5, Fig 22:

(although the above diagram shows the inverters in their transistor form rather than logical symbol)

Figure 22 is interesting because it shows a dual port register, which means that its value can be set and read from two different data bus lines. Let's ignore that though, because the 6561 only has one data bus for reading and writing. This is what makes Figure 22 relevant though, because if we ignore the second bus and focus on only one bus, then the diagram looks like this:

It appears to show the data in and data out sharing the same bus line. Later on in the same chapter (chapter 5), it shows the silicon layout (figure 22a) for the dual port register cell and it is clear that, yes, the same data line is shared for both input and output. This is relevant because in the case of the 6561, the same data line is used for both input to the register cell and output from it. The above diagram is close to what I showed in the first logisim diagram for the 6561 register cell. The obvious difference is with regards to the way that the reading is done. I've looked at this part of the die shot many times and I always come up with the same schematic. Rather than taking the output value from the point after the two inverters and connecting that directly to the data line, it instead takes the value from the point between the two inverters (so is the inverted value stored in the register cell) and then connects that value up to the gate of a pull down transistor. The drain side of that transistor is then connected to the "R"ead pass transistor. So if the point between the two inverters is HIGH (which represents the register cell storing a zero), then it pulls the data line LOW when the R pass transistor is turned on.

As I discussed in that post from the older thread, this seems to make sense only if there is a pull up somewhere along the data line that is active when data is being read from a control register. I haven't yet found such a pull up, but it feels like it should be there somewhere, otherwise the above circuit (i.e. the first one drawn in logisim) has a way of pulling the data line LOW on Read, but when the register cell is in the other state, there would be nothing pulling the data line HIGH.

Chapter 3 of the Mead/Conway book has an interesting discussion about how the charge is stored within the register cell, or more generically, how it is isolated on the input gate of an inverter's pull down transistor (the shift register sections goes into a bit of detail regarding this). Applying this to the 6561 register cell, when the data line is HIGH and W is high, then the gate capacitance of the first inverter's input is charged up. When W goes LOW, the charge is isolated on that transistor gate, and due to the feedback path through the F1 controlled pass transistor, it holds that charge indefinitely. Now when the data line is LOW, and W goes HIGH, it is designed to be HIGH at least long enough for the charge on the first inverter's input gate to discharge, which sets the register cell to be zero/low. When W goes LOW, that "lack of charge" is isolated there.