Once I decided that I was going to build a ram cartridge, I figured that I might as well make one that has ram in every hole that the vic has... BLK1-3,5 and RAM1-3. Now, that takes either four chips (32k + 3 1k chips) or 2 chips (32k + 8k) or 1 chip (64k). 1 chip is the obvious choice, but all that wasted ram just irked me.

A quick scan of Digikey for ram chips turned up no 5V 64k ram chips in stock, but a nice looking 128k ram chip (CY62128E). Being as I was already bank switching, why not switch a little more?

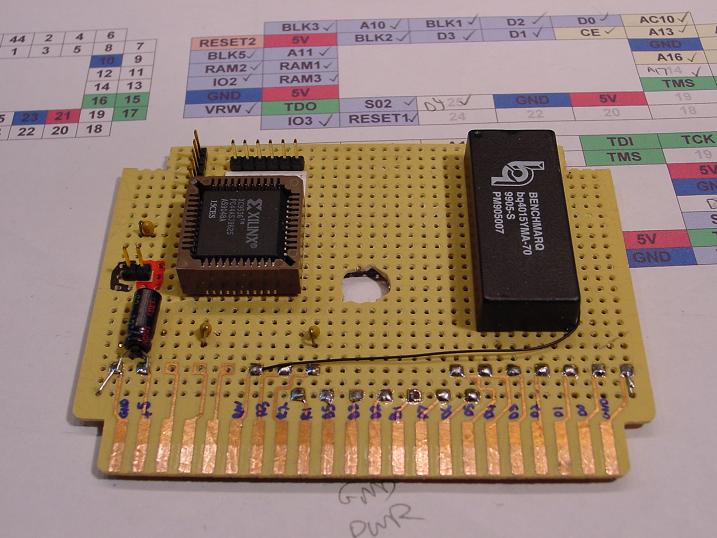

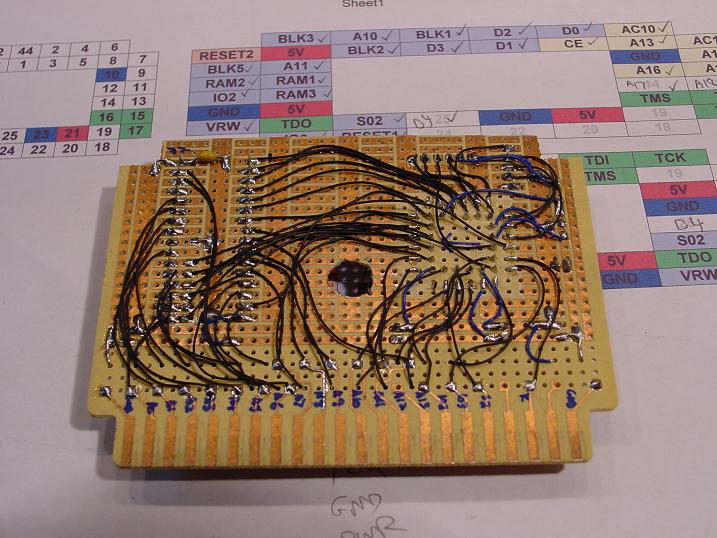

Anyhow, so my plan is to wire together a small board with a CPLD and the ram chip. I'm using a simply XL9500 CPLD to reduce the number of logic chips, and also because I've got them kicking around and not many discrete logic chips.

So the basic idea is to make the 3 1k blocks into the first 8k of SRAM, BLK1-3 into the next 8k blocks and then let BLK5 use the last 12 blocks of 8k ram. I'll latch the data lines D0-D3 and use them to provide address decoding for the BLK5 blocks. That would be latched during a write access into I02.

Memory map:

Code: Select all

SRAM Addr. Vic Addr. Notes

A10 A11 A13 A14 A15 A16 Low High Low High

RAM1 1 0 0 0 0 0 $00400 $007FF $0400 $07FF

RAM2 0 1 0 0 0 0 $00800 $00BFF $0800 $0BFF

RAM3 1 1 0 0 0 0 $00C00 $00FFF $0C00 $0FFF

BLK1 - - 1 0 0 0 $02000 $03FFF $2000 $3FFF

BLK2 - - 0 1 0 0 $04000 $05FFF $4000 $5FFF

BLK3 - - 1 1 0 0 $06000 $07FFF $6000 $7FFF

BLK5 - - D0=0 D1=0 D2=1 D3=0 $08000 $09FFF $A000 $BFFF PAGE 0

BLK5 - - D0=1 D1=0 D2=1 D3=0 $0A000 $0BFFF $A000 $BFFF PAGE 1

BLK5 - - D0=0 D1=1 D2=1 D3=0 $0C000 $0DFFF $A000 $BFFF PAGE 2

BLK5 - - D0=1 D1=1 D2=1 D3=0 $0E000 $0FFFF $A000 $BFFF PAGE 3

BLK5 - - D0=0 D1=0 D2=0 D3=1 $10000 $11FFF $A000 $BFFF PAGE 4

BLK5 - - D0=1 D1=0 D2=0 D3=1 $12000 $13FFF $A000 $BFFF PAGE 5

BLK5 - - D0=0 D1=1 D2=0 D3=1 $14000 $15FFF $A000 $BFFF PAGE 6

BLK5 - - D0=1 D1=1 D2=0 D3=1 $16000 $163FF $A000 $BFFF PAGE 7

BLK5 - - D0=0 D1=0 D2=1 D3=1 $18000 $19FFF $A000 $BFFF PAGE 8

BLK5 - - D0=1 D1=0 D2=1 D3=1 $1A000 $1BFFF $A000 $BFFF PAGE 9

BLK5 - - D0=0 D1=1 D2=1 D3=1 $1C000 $1DFFF $A000 $BFFF PAGE 10

BLK5 - - D0=1 D1=1 D2=1 D3=1 $1E000 $1FFFF $A000 $BFFF PAGE 11I banged together some quick verilog. I must have done something wrong because it ended up being easier than I though and I'm only using about a third of a XL9532 CPLD (basically the smallest one that can be found).

I wasn't 100% sure of the vic-20 bus timing though. When should I be latching data lines? I'm going to have to hook my logic analyzer up to the bus to see exactly, but it looked like data lines can be latched on the rising edge of I02? If not, I'll have to latch on the S02 clock line instead. Figured I'd keep it simple for the time being.

Once I get this running, my next step will be to interface a small pic controller and an SD flash card into it. I've done all the code for reading from an sdcard from previous projects. On the face of it, it looks pretty easy to make a generic flash cart for the vic. Basically the PIC processor would hold the VIC in reset, read a bootmenu program from the SD card and put it into BLK5 of the RAM as well as read the directory listing from the SD card and dump that also into RAM. When the VIC comes out of reset, it runs the program and lets the user select what they want to run from the flash card. When the user has selected, that triggers the PIC to reset the PIC, load the program into RAM and then passes control back to the PIC.

Anyhow, anyone see any issues with my planned implementation of a ram cart? Is there a standard for bank switching on the vic that I should be following?